Микросхемы представляют собой оперативное запоминающее устройство на 64 бит (16 слов * 4 разряда) с произвольной выборкой. Содержат 803 интегральных элемента.

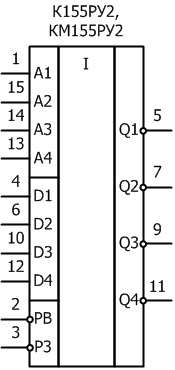

Назначение выводов:

1 — вход первого разряда A1;

2 — вход разрешения выборки PB;

3 — вход разрешения записи;

4 — вход данных D1;

5 — выход первого усилителя Q1;

6 — вход данных D2;

7 — выход второго усилителя Q2;

8 — общий;

9 — выход третьего усилителя Q3;

10 — вход данных D3;

11 — выход четвертого усилителя Q4;

12 — вход данных D4;

13 — вход четвертого адреса A4;

14 — вход третьего адреса A3;

15 — вход второго адреса A2;

16 — напряжение питания.

Электрические параметры:

Номинальное напряжение питания . . . . . . . . . . . . . . . . . . . . . . . . 5 В ± 5%

Выходное напряжение низкого уровня в режиме

хранения «Н» в невыбранных адресах . . . . . . . . . . . . . . . . . . . . . ≤ 0,4 В

считывания . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ≤ 0,4 В

Напряжение блокировки . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ≥ -1,5 В

Входной ток низкого уровня . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .≤ -1,6 мА

Входной ток высокого уровня . . . . . . . . . . . . . . . . . . . . . . . . . . . . .≤ 0,04 мА

Входной пробивной ток . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ≤ 1 мА

Выходной ток высокого уровня в режиме считывания при

хранении «Н» в невыбранных адресах . . . . . . . . . . . . . . . . . . . . . . ≤ 20 мкА

Выходной ток высокого уровня в режиме считывания . . . . . . . . . . .≤ 20 мкА

Выходной ток в режиме хранения . . . . . . . . . . . . . . . . . . . . . . . . . .≤ 20 мкА

Ток потребления . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .≤ 105 мА

Потребляемая статическая мощность на 1 бит . . . . . . . . . . . . . . . . ≤ 8,6 мВт

Время восстановления усилителя считывания после

записи низкого уровня . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ≤ 70 нс

Время восстановления усилителя считывания

после записи высокого уровня . . . . . . . . . . . . . . . . . . . . . . . . . . . . ≤ 70 нс

Время выборки разрешения для перехода из состояния

низкого уровня в состояние высокого уровня . . . . . . . . . . . . . . . . . ≤ 50 нс

Время выборки разрешения для перехода из состояния

высокого уровня в состояние низкого уровня . . . . . . . . . . . . . . . . . ≤ 50 нс

Время выборки адреса для перехода из состояния

высокого уровня в состояние низкого уровня . . . . . . . . . . . . . . . . . ≤ 60 нс

Время выборки адреса для перехода из состояния

низкого уровня в состояние высокого уровня . . . . . . . . . . . . . . . . . ≤ 60 нс

Время задержки выключения от входа разрешения выборки

до выхода усилителя считывания . . . . . . . . . . . . . . . . . . . . . . . . . . ≤ 50 нс

Время задержки включения от входа разрешения выборки

до выхода усилителя считывания . . . . . . . . . . . . . . . . . . . . . . . . . . ≤ 50 нс

Время задержки выключения от адресного входа

до выхода усилителя считывания . . . . . . . . . . . . . . . . . . . . . . . . . . ≤ 60 нс

Время задержки включения от адресного входа

до выхода усилителя считывания . . . . . . . . . . . . . . . . . . . . . . . . . . ≤ 105 нс